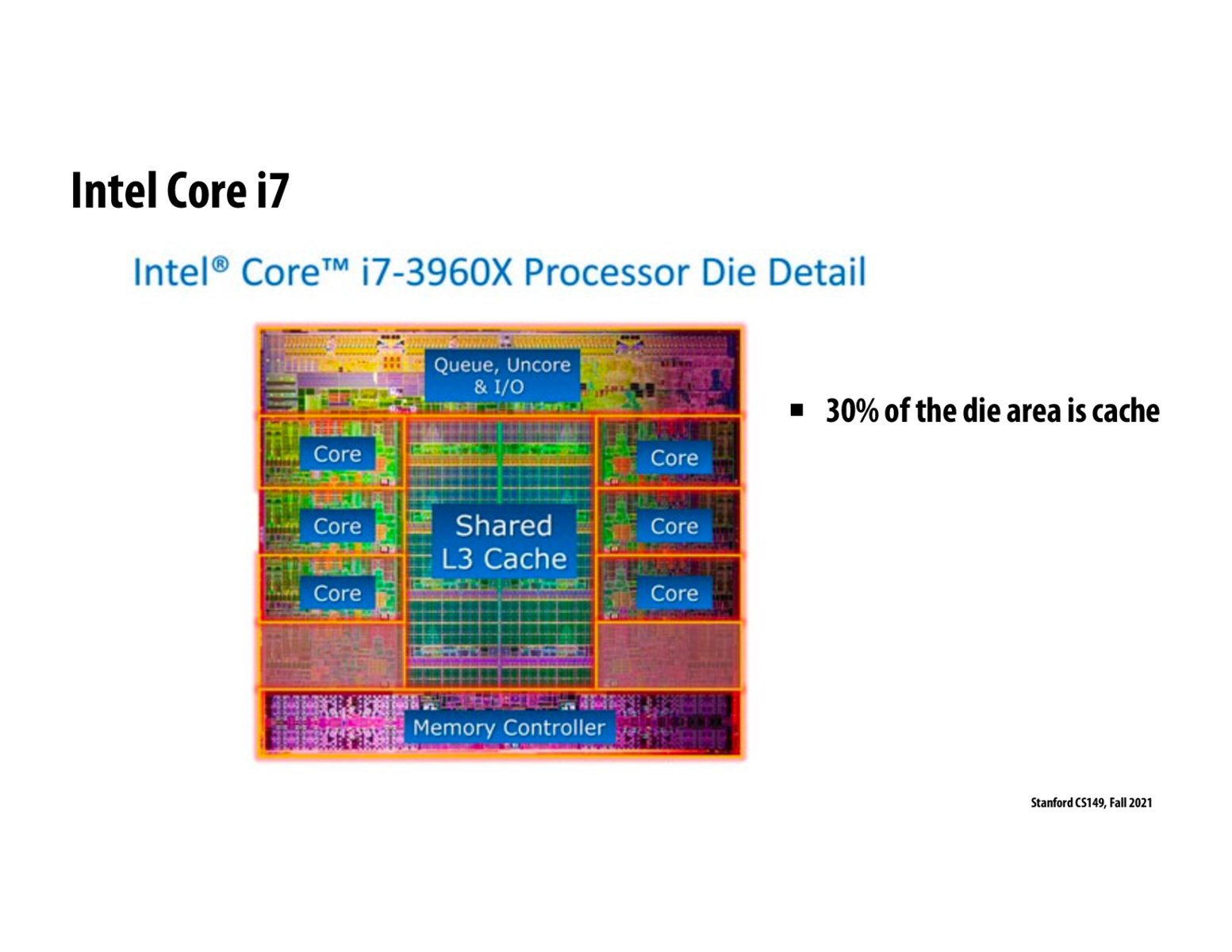

A review of caches: the point of caches is to exploit the inherent temporal and spatial locality of memory access to retrieve data with less latency and higher bandwidth. In a modern CPU you often get a cache hierarchy. My understanding is that lot of memory loads don’t hit the cache and can try the next cache in the hierarchy.

@jennaruzekowicz

Main memory is: - DRAM (high density, cheap, slow) - physically distant from chip, on the scale of 10's of cms) Cache memory is: - SRAM (lower density, more expensive, fast) - physically closer (on chip) - as far as I know, the closer it is to the actual execution-bits of the core, the lower density it is (which allows for bigger and more power-hungry, but faster components)

Regarding memory 'size': there's a difference between physical size (i.e. size in silicon) and logical size (e.g. size in bits). While overall they're correlated, they're not exactly the same, and density (logical size/physical size) is a somewhat useful indicator of speed.

As a general rule larger implies higher latency, but at precise levels (i.e what you're asking about in your question), the nuances are complex enough that it's hard to say.

Distance to processor always matters, and after a certain point, the physical size of the memory is going to play into that distance, and I've heard that lower density memory can allow for bigger, and more power-hungry components (e.g. transistors, conductors) that can give lower latency up to a certain point (you might see this in L1 v. L2, for example), but beyond that is the domain of EE majors, among whose number I am not counted.

Please log in to leave a comment.

Maybe I have a misconception of a cache, but can anyone further explain the difference between the cache and main memory when it comes to size? The cache appears to be much smaller. However, as I look at chips, we seem to be making the caches larger and larger. Does data access become slowed with larger caches? Is that one of the reasons we have issues accessing main memory quickly? OR, does it simply have to do with distance from the processor? In summary, does size impact number of cycles to fetch and how do we combat cache sizes increasing?