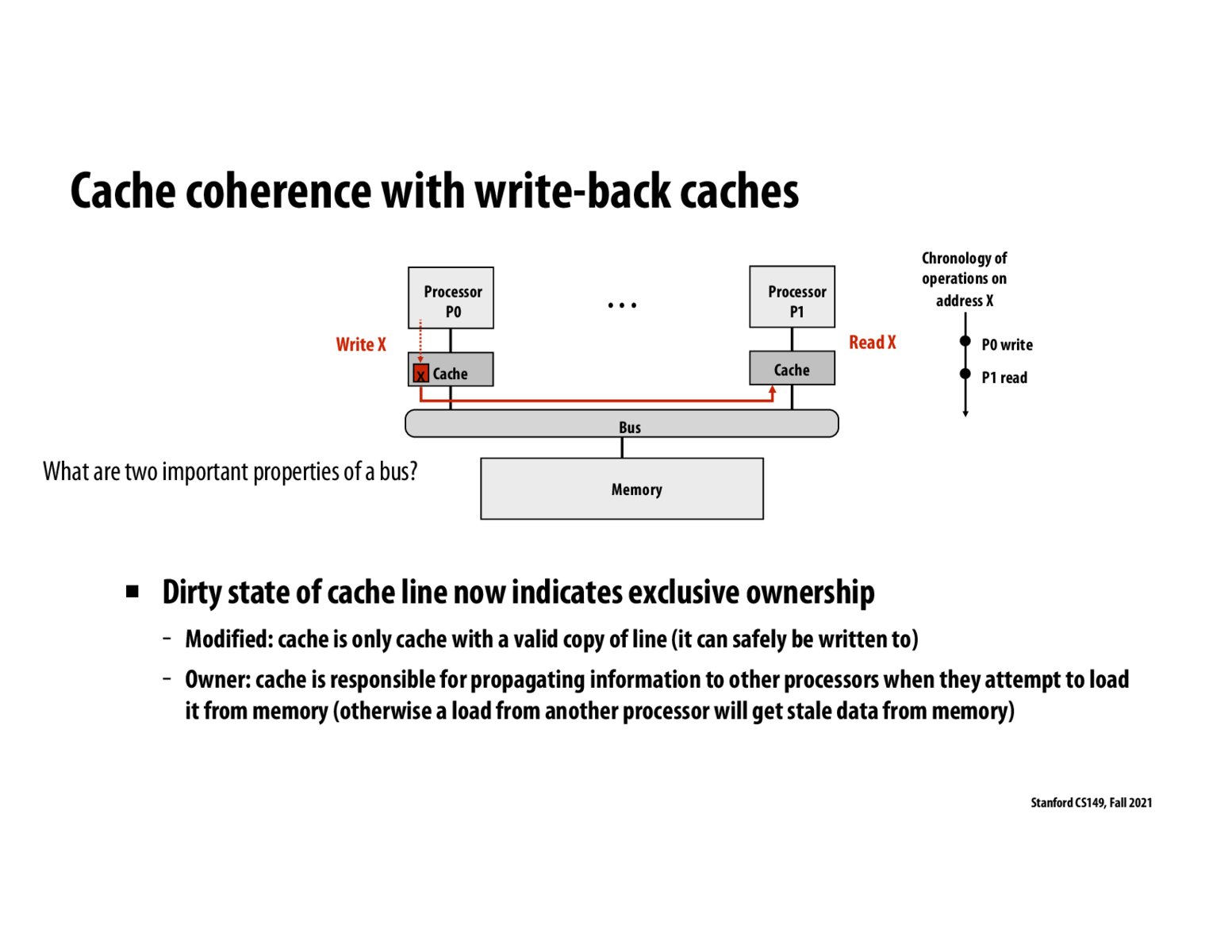

I've never know when a "bus" meant before, as I'm just a CS student who hasn't taken any hardware or computer engineering courses. Is a bus just a type of interconnect with the properties wkorbe said? Or are we expected to know more about busses somehow?

Where does the temporary memory locate for a "write-back" cache?

Is there any race condition with communication on the bus? For example, would the following situation happen: - P0 writes to a shared memory location, protected by a lock - P0 releases the lock - P1 acquires the lock - P1 reads from a shared memory location <-- is it guaranteed that by the time this happens, the invalidation from the bus has already reached P1 for the memory location P0 wrote to?

I don't think temporary memory is needed in the case of write-back cache but I could be wrong though. The data stored in the cache is only written back to main memory after it is replaced.

Hardware related question: what is actually doing the communication and managing the BUS? Does this require its own processor of sorts?

How exactly is the bus implemented? Is this something that is managed by some layer of abstraction on the programming side or is it mostly actually dependent on the architecture of the hardware? Like how does someone creating system code for this device actually use the bus and what logic is involved?

This link here has some simple high level information about the Bus component: https://www.techopedia.com/definition/2162/bus

Summary: In a network, the “bus” is a digital structure that will transmit data in either parallel bus or serial bus format along a set of nodes.

Is a write-through cache always more expensive? It seems like here there's a lot of communication cost in communicating to the other processors that the cache line is now invalid

@potato, wouldn't that communication need to happen even if we used a write-through cache?

Please log in to leave a comment.

Two important properties of a bus: serialized operations and broadcast medium.

Snooping is often called "Bus Snooping".