A comment access pattern in many programs is to read data and then later write to it. For example:

if (x > 0) {

x++;

}

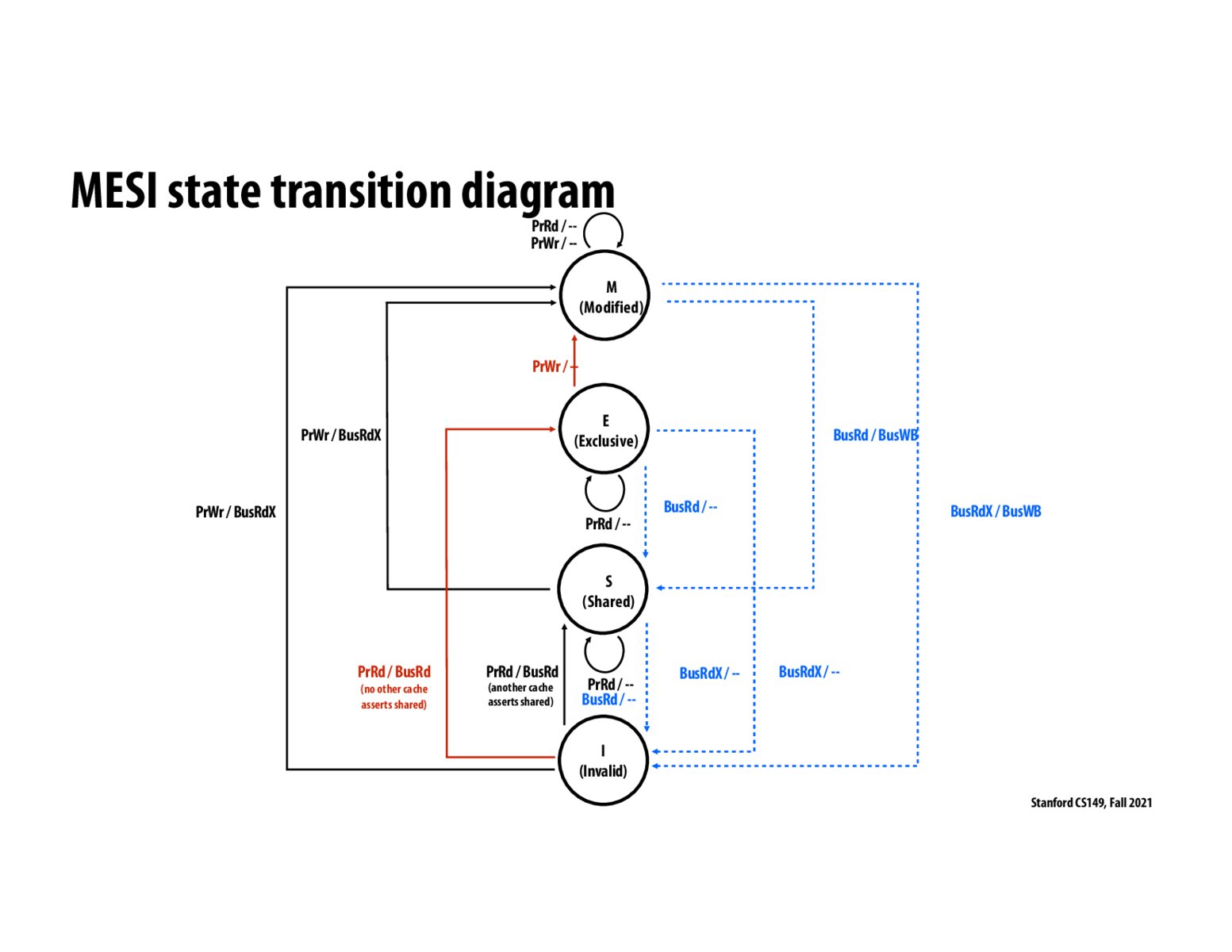

To MESI allows the original load to move the line into the E state. (this requires notifying the other caches of the intent to read) And then the subsequent write can elevate the line to M without notifying the other processors. (Since, by definition of the E state, no other processors have the line.)

If this was MSI. The first read with trigger an intent to read message and movement from I to S. The later write would trigger an intent to write message and movement from S to M.

I think the assumption here is that in most programs we do not expect processors to access same piece of memory at the same time. Therefore, in majority of the case, we can use E state to reduce the amount of information needed to be sent through buses when we want to write into the memory

Please log in to leave a comment.

still seems to me that cases where E state occurs is going to be just a fraction of the M+S+I states. Is it then a lot of benefit to have the overhead of maintaining this extra E state?