I think that there are ways to deal with this, as explained in the following slides, the hardware concept of Fence is one of these ways.

I wonder what some low level optimizations to the write buffer there are. For instance, is there no equivalent dirty bit we can use so that we can ensure consistency across processors?

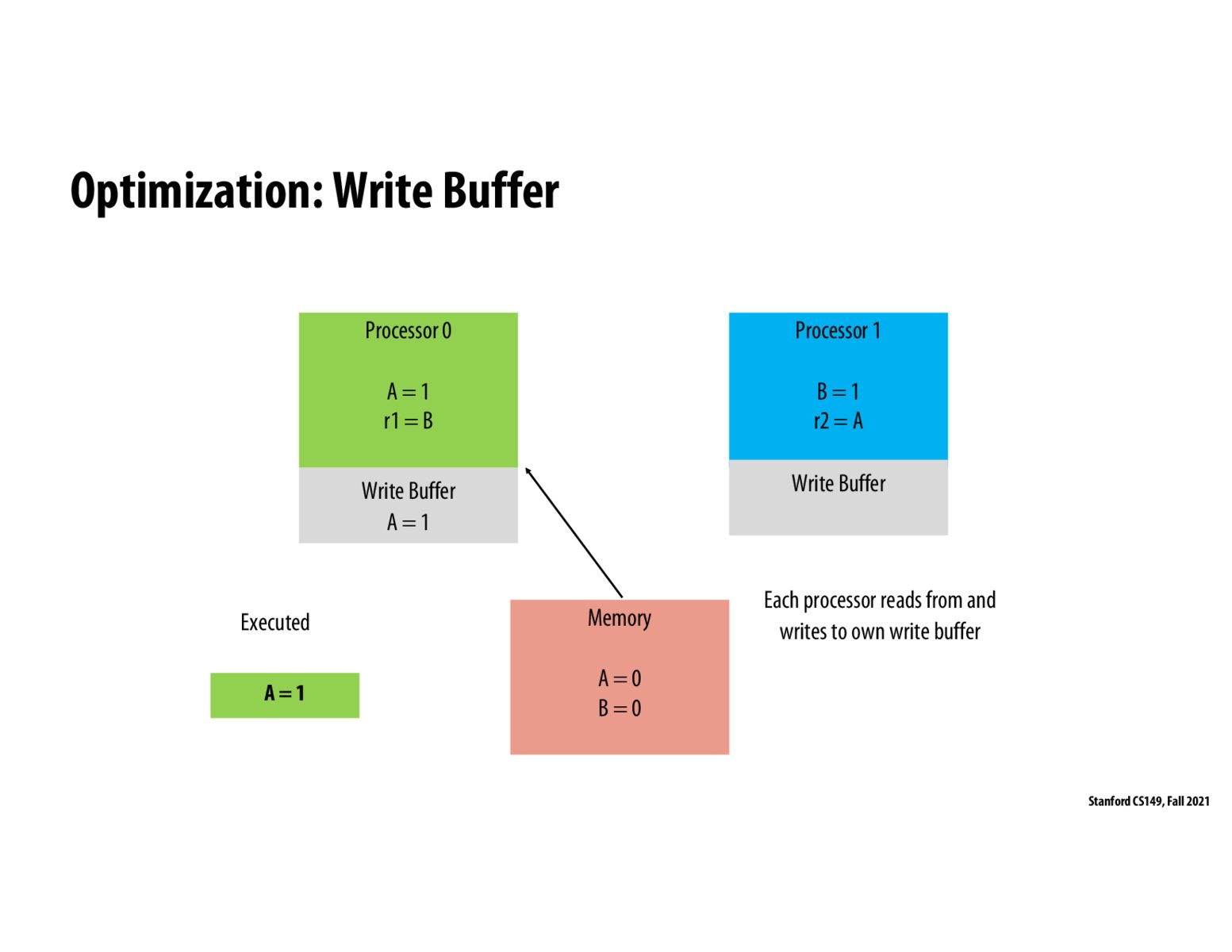

Wasn't sure what a write buffer was at first, so a few notes (largely from Wikipedia + Q&A from lecture): - Type of data buffer used to "queue up" / send writes to main memory or to next layer in memory hierarchy - This frees up the cache (and, maybe memory system as a whole?) to service read requests while the write is happening -- subsequent reads can happen w/out waiting for long memory latency writes. This kills sequential consistency within a thread of execution; subsequent reads can execute before a preceding write commits. - A buffer has space for multiple writes to be queued in the write buffer; when all slots are full, subsequent writes have to wait until slots are freed (so, eventually you might get stalls) - If a write is in a write buffer, it hasn't "happened" yet -- no other processors can observe it; it's on its way to memory but hasn't gotten there yet. Writes "come out of" write buffers in a hypothetical sequential order.

(lol oops meant for those to be bullet points; formatting did not happen.)

If we combine a write buffer with synchronization, we should then regain sequential consistency. So for synchronized data the write_buffer doesn't bring any optimization, but it then gives the programmer more control as the default standard will be optimized without sequential consistency and we can enforce it when necessary.

I am a bit confused why r1 and r2 are not considered writes if we are setting them.

Had the same question as martigp@, and I try to convince myself that r1 and r2 refers to registers (as opposed to memory here)

In the case of two write buffers writing to the same variable, how do we handle that since each thread does not know the other threads' write buffer?

I'm guessing that we'll probably need some synchronization/mechanism to lock a variable and maybe stall the other thread? I think we went over something like that in cache-coherency with how only 1 processor can be in the exclusiveWrite state and I'm guessing maybe memory works similarly.

Please log in to leave a comment.

With a write buffer, we are uncertain about when the write stored in the buffer will be visible to other processors. Hence, this leads to some potential issues, right? As programmers, are we responsible for protecting the program from having this type of execution, or there exists built-in command to stop this from happening?