That's a good point. Some more information: In computer architecture, load instructions are much more critical than store instructions. If the load dependencies of an instruction are not satisfied, that instruction cannot run. Load instructions are the bottleneck of processors.

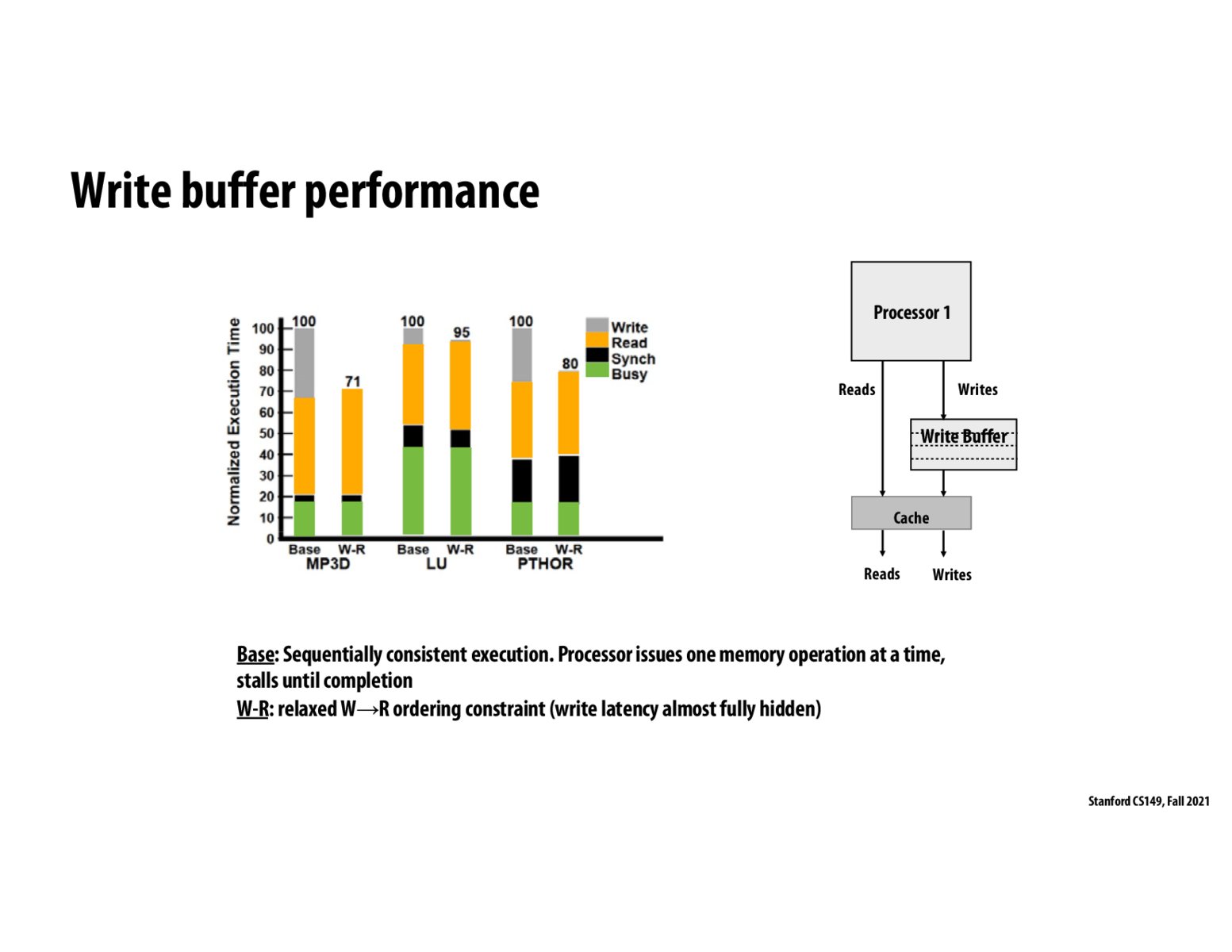

That is why, it is important to prioritize reads over writes, so that the program can continue to execute smoothly. We perform read operations as soon as possible, and perform the write operations as and when possible ("lazy write"). This helps to "hide" the latency for write operations.

What is the LU program and why does it not achieve too much optimization from W-R?

How does WR relaxed help hiding write latency? This means that we can read prior to a write being written into memory. So this implies that we can go on with our reads without waiting for our stores/write latency stuff to finish, which is how it hides latency. But what about the case where there are many stores and many reads from the same variable? Wouldn't this be super prone to error?

Please log in to leave a comment.

It is mentioned in the slide, but to emphasize on it, W-R relaxed helps with hiding write latency.