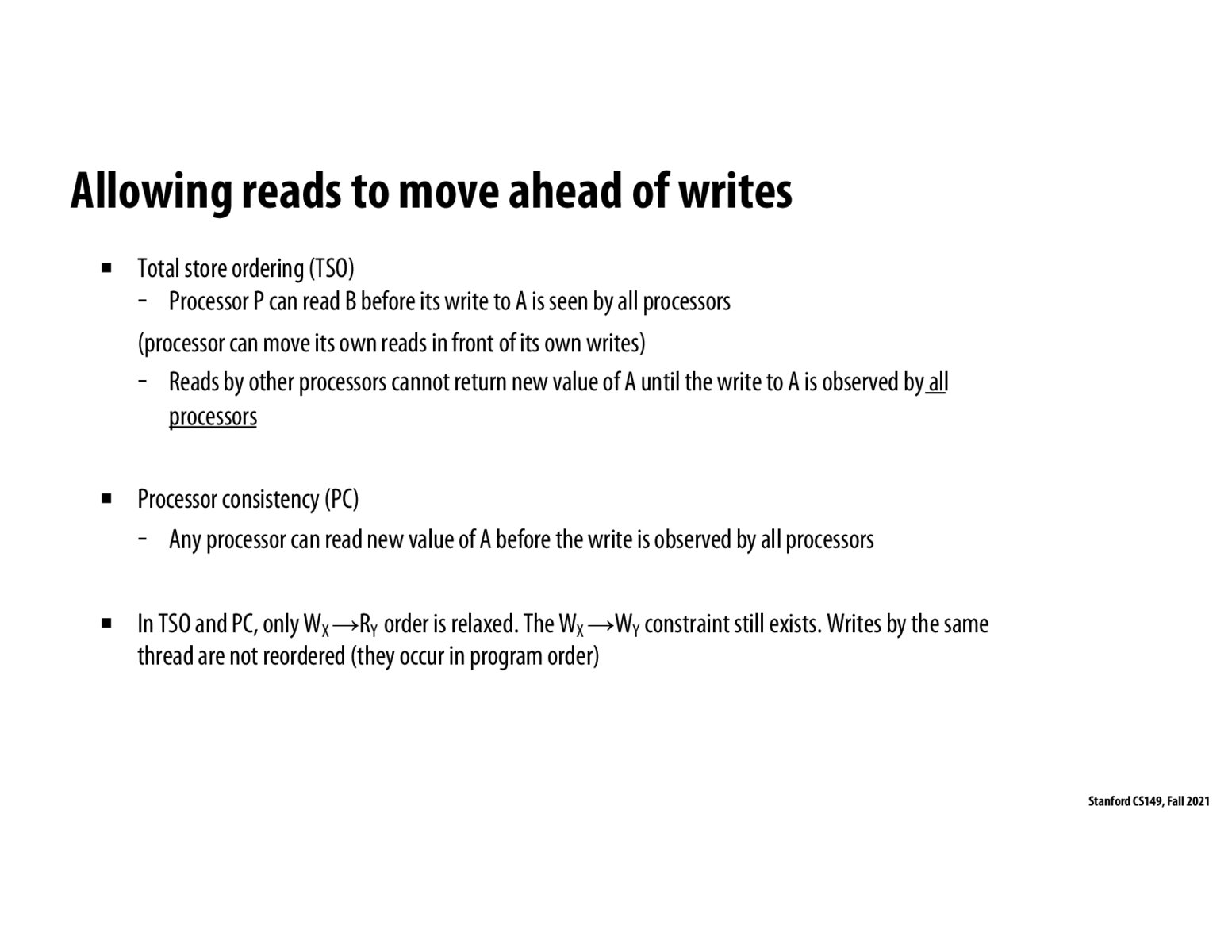

I have similar questions to @juliewang about this slide. I think what initially confused me was that I couldn't figure out the reason why the processors needed to behave the way that they did for TSO. After some more thought, I realized that this slide could be viewed more abstractly by remembering that these memory consistency models (e.g. TSO, PC) simply define the behavior of reads and writes and the ordering of these operations viewed by the different processors in the system, so in this context TSO and PC are simply a set of rules that were agreed upon (for some reason) which define a memory consistency model. I imagine there is a reason that TSO was defined the way that it is, but I think it's also beneficial to take a more abstract view of this slide as showing different ways you can relax the memory consistency models (since TSO and PC both relax the Wx->Ry order, but are different models of memory-consistency since they have a different set of rules).

I also find it somewhat confusing that the Total Store Ordering dictates the ability of other processors to read memory where Memory Consistency has up to this point seemed to only focus on determining ordering within a single processor. However, after tracing through possible orderings with TSO ordering it is clear that it does simplify the number of possible orderings.

@juliewang, @ardenma, @terribilis The definition of memory consistency (slide 23) concerns behaviors of reads and writes to different locations as observed by other processors. Memory coherence is also a multi-processor concept. Essentially we want all the processors to agree on the same value of the variables.

@juliewang Memory consistency doesn't necessarily mean that it is relevant to strictly one processor. It could depend on how different lines interact with each other across different cores. So it might matter because two processors might be using different values of A.

Please log in to leave a comment.

So in Total Store Ordering, why cant the other processors read the new value of A until the write to A is observed by all processors? I thought that that Memory consistency was only concerned with the order of operations as observed by other processors on a single processor. Why do the reads of other processors matter here? Don't we only care about the fact that other processors can see that processor P might complete it's read before the write it issued?