*unexpectedly

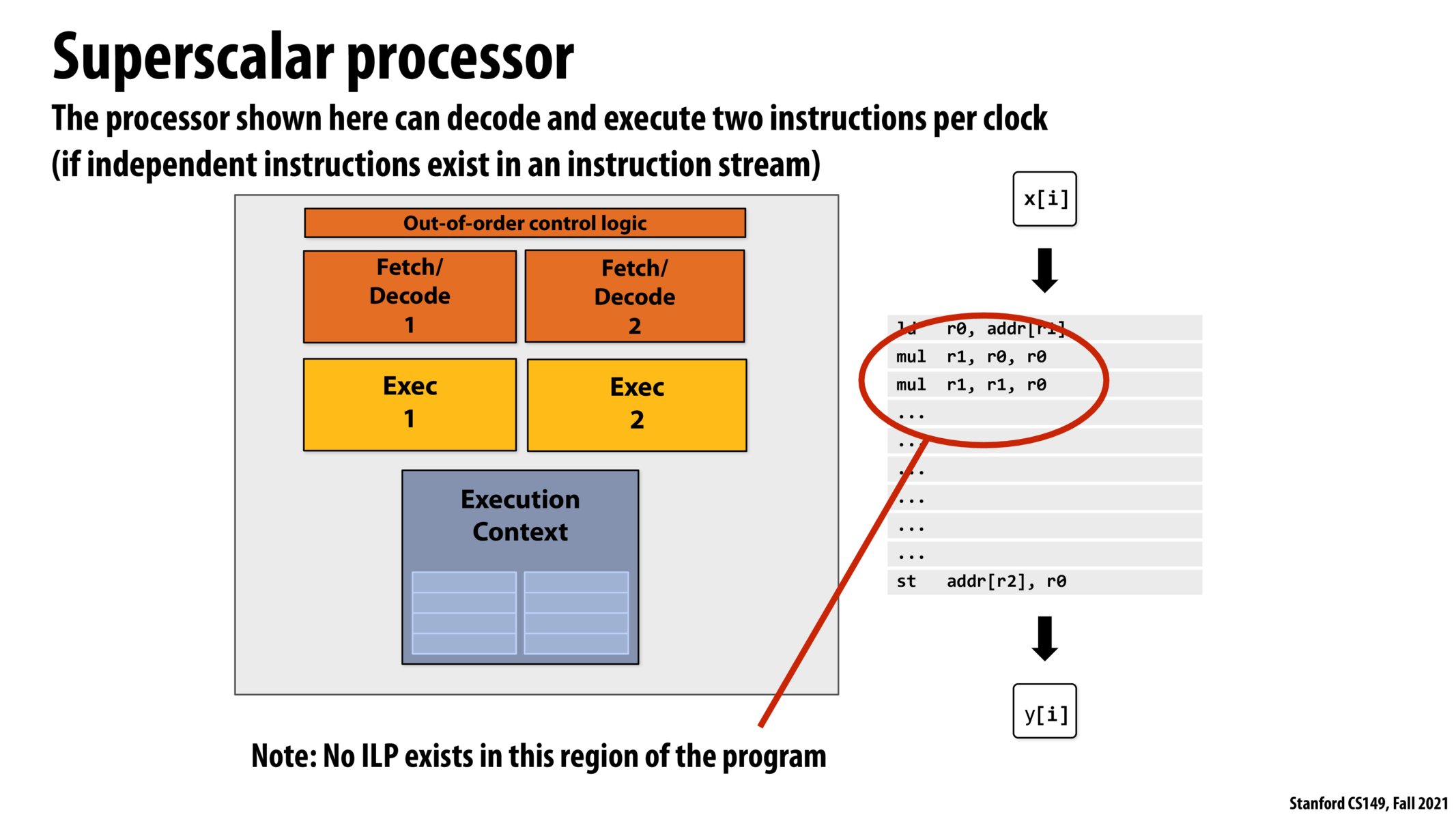

@jchao01 As the note says at the bottom of the slide, there’s actually no ILP for the displayed instruction stream region. This is precisely because of the dependency between the instructions. Also, I’m not too sure what you’re saying about overwriting r0...the two mul instructions both store their result in r1.

We know that the execution units execute the instructions fetched by the fetch/decode unit. We also heard during lecture that the # of fetch/decode units and the # of execution units are not always the same. Then, if we had 1 fetch/decode unit and 2 execution units, can we still only run 1 instruction per clock (since we can only fetch 1 instruction per clock) despite having 2 execution units?

Regarding "can we still only run 1 instruction per clock (since we can only fetch 1 instruction per clock) despite having 2 execution units", my two cents are

- Whether two execution units are both busy is application specific; if there are opportunities of instruction-level parallelism, and together with instruction pipelining, two ALUs might be busy in the same clock.

Where does all the logic happen for finding independence within instructions and such? Are there separate ALUs and registers not depicted in these hardware drawings which do this instruction scheduling? Or does everything happen within the 'fetch / decode' section of the chip? Or entirely elsewhere? It seems very meta that a very powerful computer is required just to run a computer.

@rthomp, I believe this logic happens in the "out-of-order" control logic box depicted at the top of the diagram.

Please log in to leave a comment.

I'm still confused about to what extent ILP could be applied here. Mainly, (if the processor had more exec units) could the processor simultaneously execute two ld instructions here to reduce minimize memory stall time? My thinking is that it wouldn't be able to because the processor doesn't know exactly how long the memory operation would take, and if it is completed earlier than expected, it could expectedly overwrite r0 before it is used as a dependency for other operations.