Back to Lecture Thumbnails

tonycai

ckk

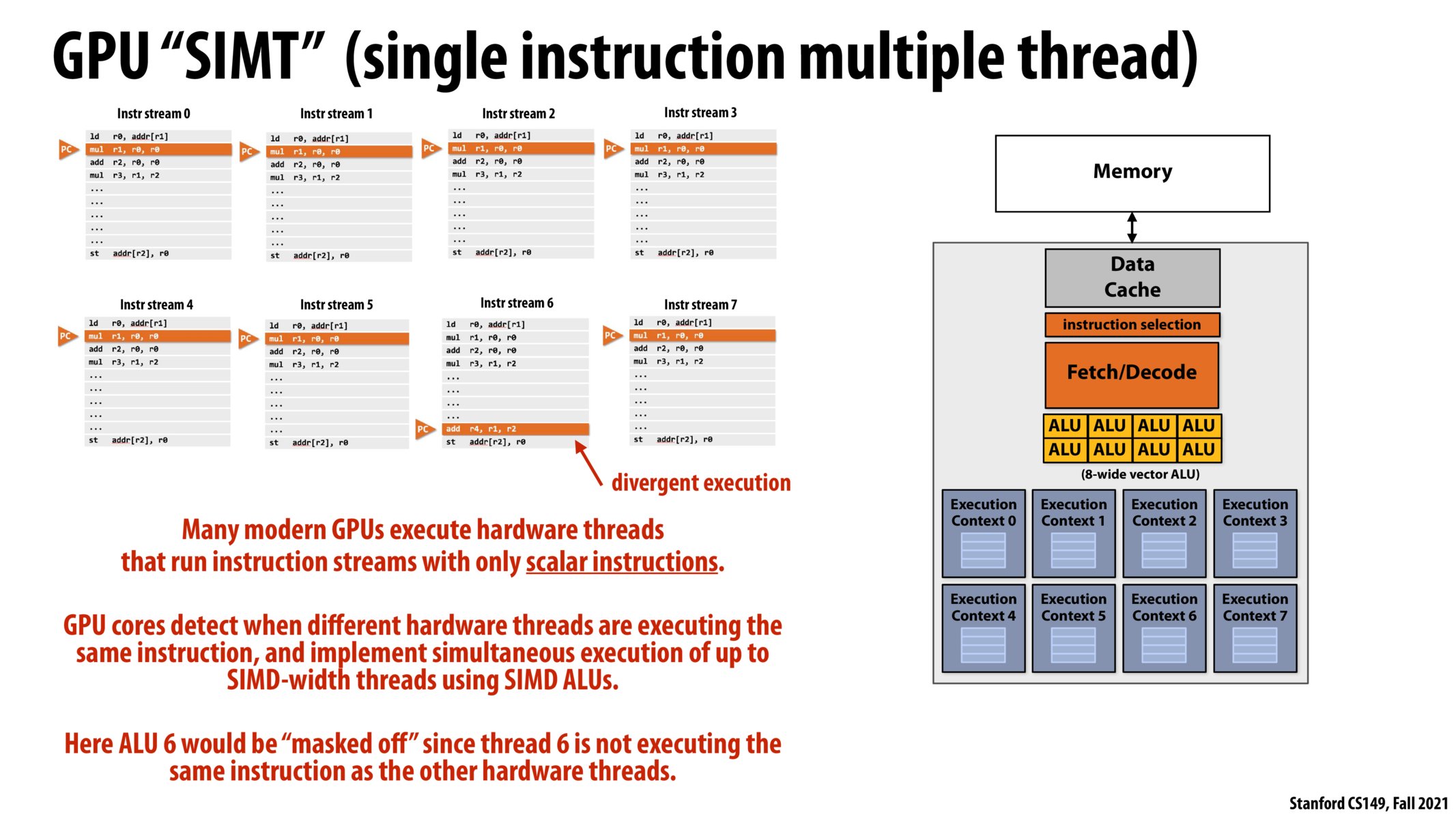

Just wondering, which part of the SIMT CPU detects when hardware threads are executing the same instruction? Is that a new part outside the scope of this class, or is it the Instruction selection/fetch and decode unit?

sanjayen

@tonycai, yes I believe so. I would imagine that some part of the GPU architecture (either in the fetch/decode unit or in the execution context) has access to each of the instruction streams (perhaps via an instruction pointer). Some unit in the GPU must then be comparing instruction streams and optimizing to use SIMD execution units.

Please log in to leave a comment.

Copyright 2021 Stanford University

IIUC in the GPU SIMT architecture, multiple threads share the same SIMD for arithmetic operation. Though since there's only one fetch/decode unit, how would it handle divergent execution?