I'm slightly confused about how we determine the hypothetical serial order. Isn't the order among different processes non-deterministic?

This is a really important concept.

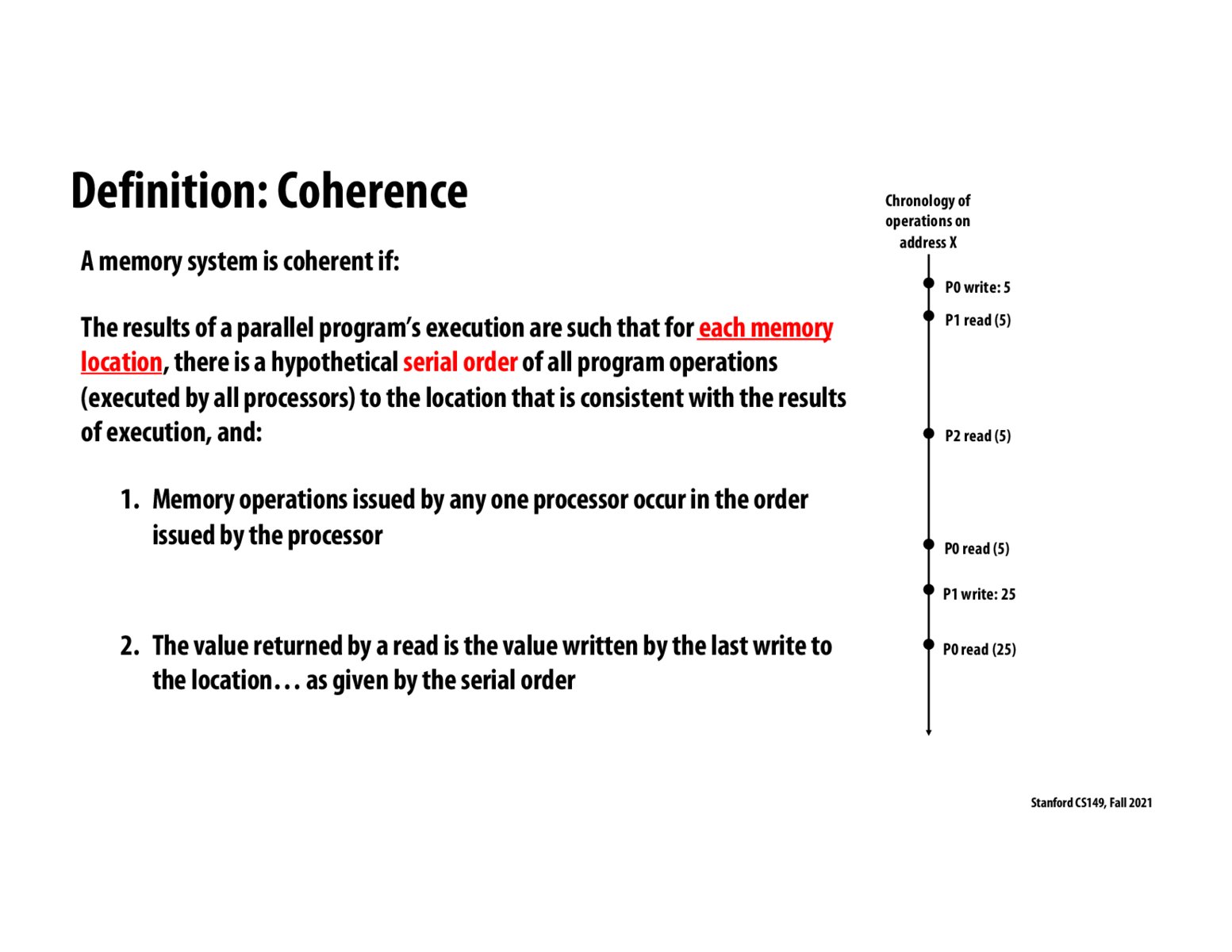

The idea is that in a coherent memory ALL PROCESSORS must agree on some order of operations to the address in question. In other words, if we look at the values returned by loads by all processors, there is some timeline that orders all the writes/reads to an address that would explain all the observations by all the processors.

For example, if processor 1 observed "3" from load A. Then wrote "4" to A. Then observed "5" from a later load of A, then we can't have processor 2 observing "4" from a load of A, then later writing "5" to A, and then later observing "3" from a load of A. There's no single timeline of loads and stores that would explain those results.

I understand that we have to establish some serial order for all the memory operations at an address across all the processors, but how do we get this hypothetical order? If it's not time-based, then how do these operations get serialized?

From what I understand, this is more of a theoretical concept where a memory system is coherent if there exists this ordering. The actual ordering for a memory location can then be determined by the coherent memory system.

Please log in to leave a comment.

Kayvon's useful comments from lecture: