Back to Lecture Thumbnails

ggomezm

shaan0924

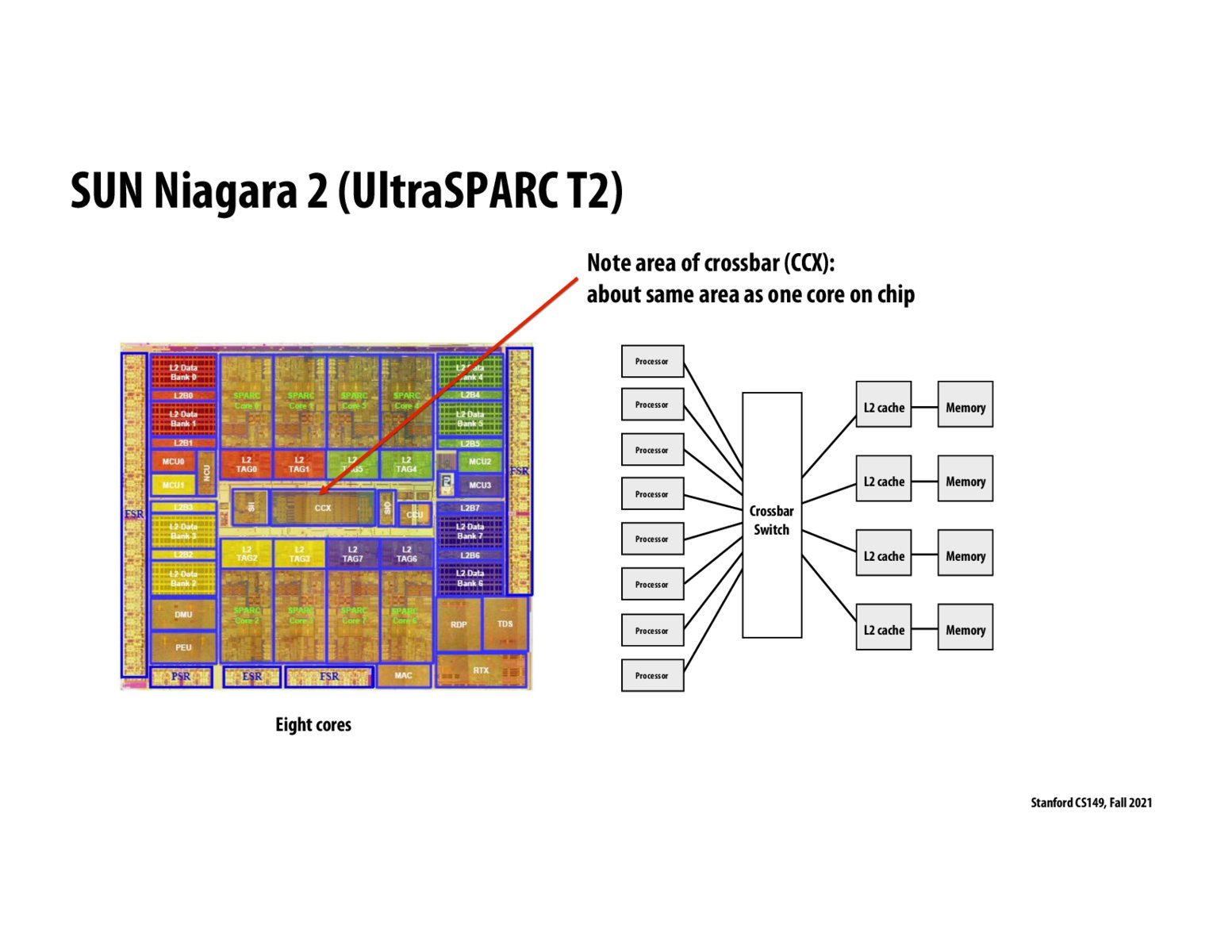

If the crossbar is the shared cache between all the cores, why are there separate L2 caches as well? Would it be more efficient to have the L2 cache also be shared amongst the processors to avoid multiple same states?

gomi

I think the crossbar here is to facilitate the communication and bandwidth of the shared cache (L1 caches on each processor and an array of L2 caches). The processor blocks on the left would each have their own L1 caches.

Please log in to leave a comment.

Copyright 2021 Stanford University

So here the crossbar is a shared cache between all cores?