Agreed, the cache controller is the unit that appears to perform the operations described by the MSI model's automaton. I wonder how the hardware underlying the cache controller works and also what happens if a single cache controller "breaks" (I'm imagining a fault tolerance scenario on a computer with many many processors). However, since this would be a hardware issue, I'm not sure what preventative measures can be put in place.

I agree that the Cache controller is responsible for maintaining the MSI protocol. It is an interesting design, because it does seem to introduce a single point that challenges fault tolerance. As data requests must go through it. I would be interested to know what is done to improve fault tolerance.

Please log in to leave a comment.

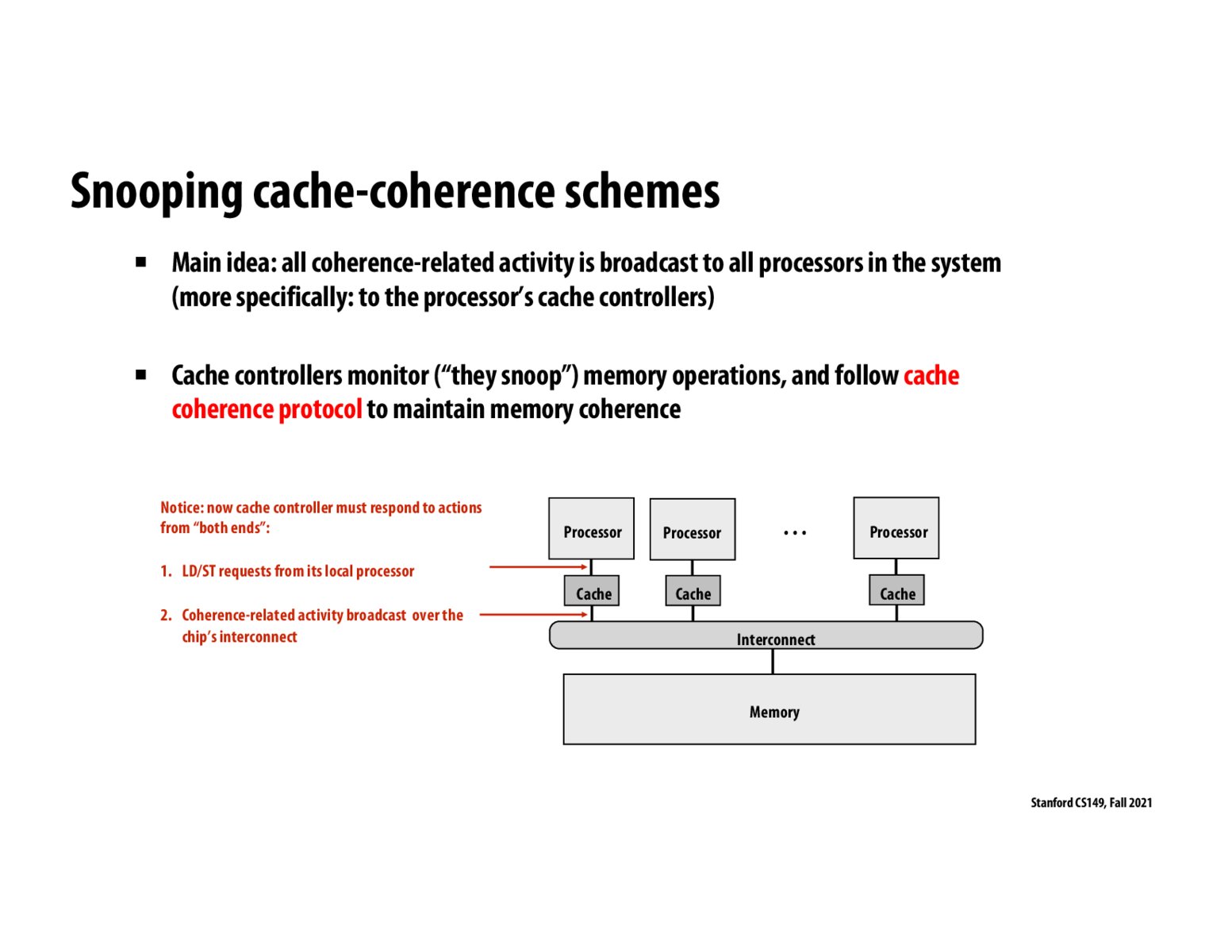

The diagram seems to indicate that "snooping" is handled by the cache controllers, which broadcast instructions on the interconnect bus (serially, as per the state diagram in the later slides) and respond to the LD/ST requests from their local processors after the serial execution on the bus is complete (and their local cache has dirty bits set appropriately).