Back to Lecture Thumbnails

evs

schaganty

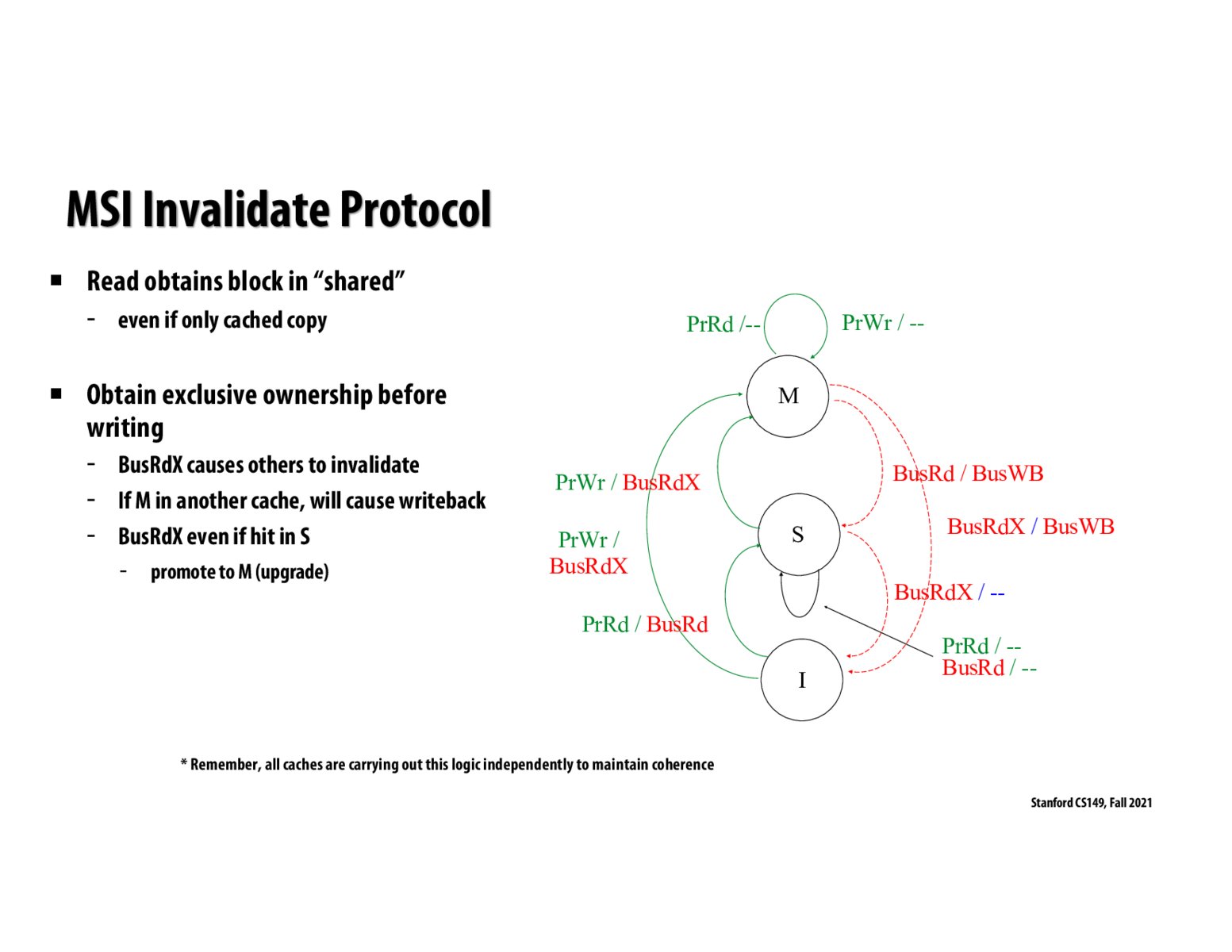

@evs, when cache A contains a cache line that's in the Modified or Shared state, and another cache B writes to the same address, cache A's cache line is now invalid (this means that it no longer reflects the most recent update to that memory address).

When cache B writes to an address, it broadcasts a BusRdX message to the other caches using the shared message bus. When other caches receive this message and they have a cache line corresponding to that same address in their cache, they invalidate it.

If the other caches want to read that memory address again, they'll read it from cache B since they know that cache B contains the most recent update.

Please log in to leave a comment.

Copyright 2021 Stanford University

Unsure about when the invalid state is triggered. How do other caches know that their copy has become invalid?