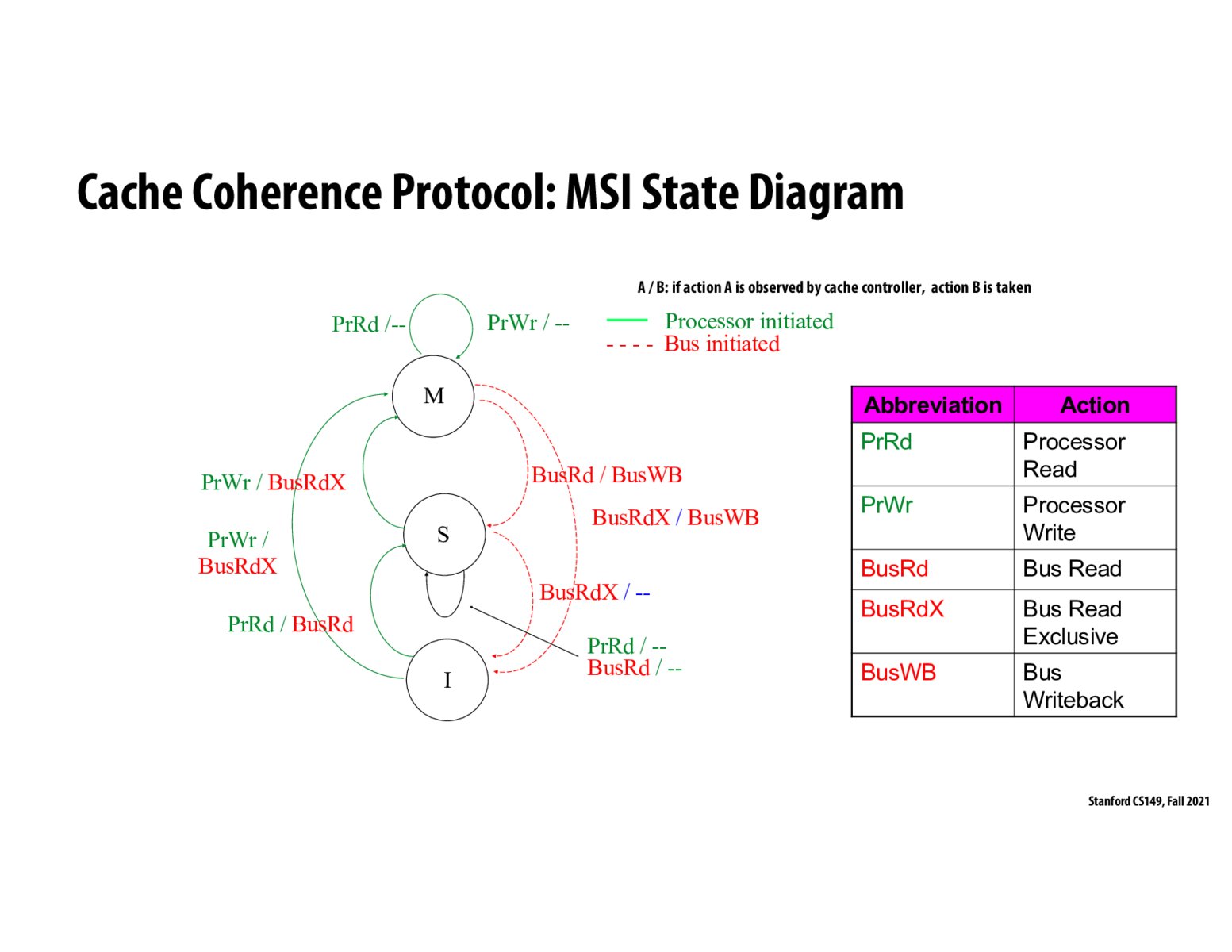

When a cache receives BusRdX from ANOTHER CACHE, it must invalidate its copy of the line as per the coherence protocol. If the line is in the modified state, it much flush the contents of the line back out to memory prior to invalidating, otherwise, the updated data in the modified line would be lost.

What if two processors try to update the same cache line at the exact same clock cycle? How do we determine who gets transitioned to the M state first?

@fdxmw I believe that the professored mentioned one of the features of bus is that it serializes transactions. So when two processors try to update the same memory address at the exact same clock cycle, the bus system will probably figure out a way to break ties, and issue one BusRdx and then the other. The processor corresponding to the first BusRdx transaction should transition to the M state first. Since the two writes happen at the exact same clock cycle, choosing either ordering should be fine, since if the ordering of writes will impact the program's correctness, the programmer should have implemented some sort of synchronization to order the writes.

To be clear, a processor in the M state only ever writes back data to memory, and only ever transitions to the I state, when ANOTHER processor asks to read and issues a BusRd or BusRdX, correct? It can keep issuing its own processor writes and overriding data without having to immediately write it back to memory?

@rthomb. Correct!

If the state of the cache line is not changed, no other caches need to know!

Worth noting that any bus action in the M state results in the line no longer being in the M state, because it means another processor must be seeking to either read or write that cache line.

This diagram really helped me understand how processors interacted with the cache for different types of action. For instance, a processor write from invalid cache state produces a Bus Read Exclusive that brings the cache to the modified state, while a processor read in the shared state keeps the cache in the shared state still.

@jasonalouda, this also happens in the modified state when the processor holding the cache line issues a read or write.

Please log in to leave a comment.

Why does processor write back the cache line to memory in modified state upon BusRdX, prior to transition to invalid state? If there is another source of recently modified data from a processor, I don't think we need to flush the cache to memory.