^ wondering the same thing.

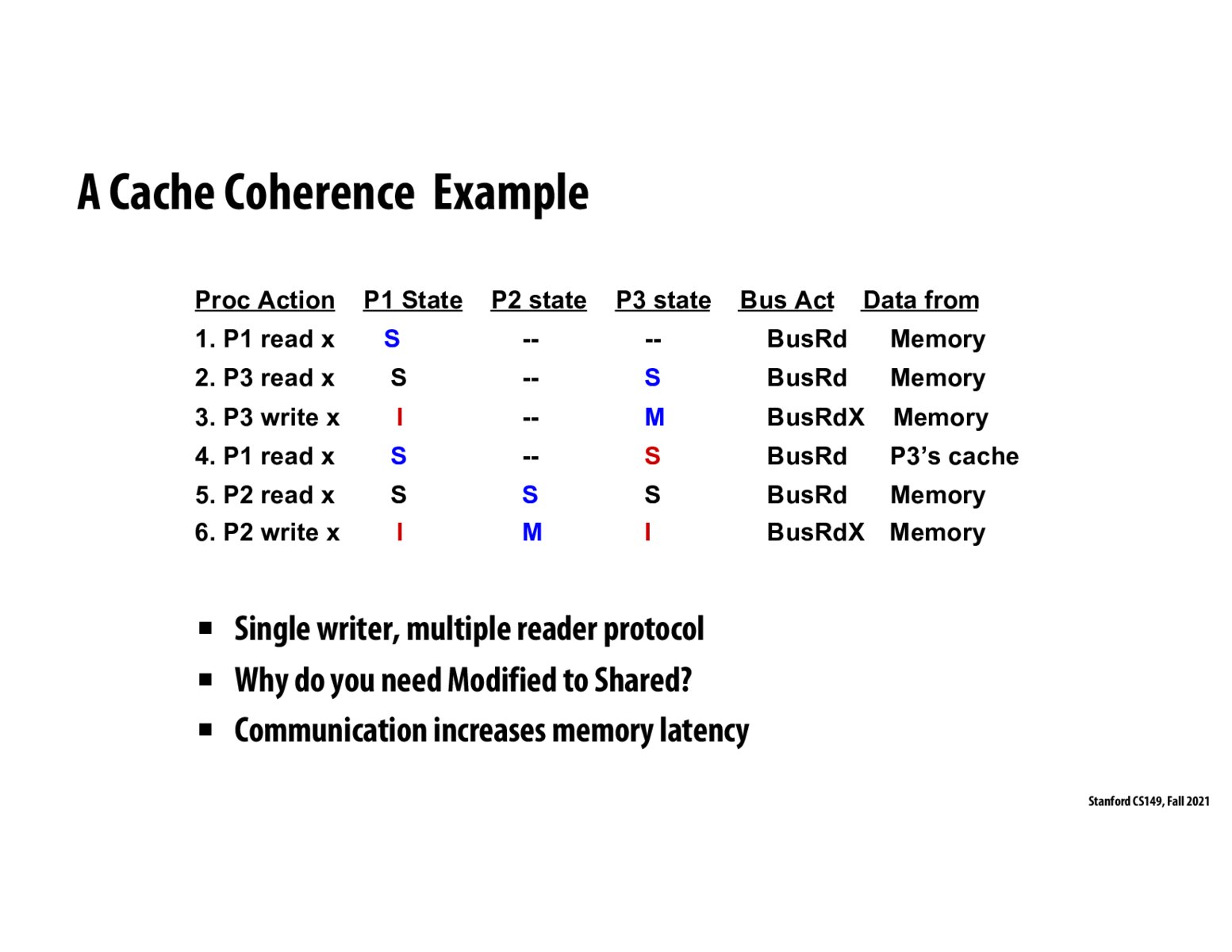

In step 2, the data is read from memory but for the same transaction in step 4, the read is from P3's cache?

I'm not quite getting what the difference between BusRdX and BusWr is, could someone explain? Thanks!

@amagibaba BusRdX will read the line with intent to modify. It must invalidate all other caches copies. BusWB is a writeback operation where the cache controller puts contents on bus and updates the memory.

@shivalgo I think step 4 reads from P3's cache because P3 is in Modified state and it holds the latest copy. Reading from memory would be wrong (i.e. reading stale values).

I think we need modified to shared because after the processor modifies state, it is no longer modifying the cache line, so that gives other processors chance to share the new cache line with the original processor

With a single-chip multi-core system, there is a single clock driving all of the processors on the chip

From the perspective of the processor in the Modified state, we need a Modified to Shared transition to tell it not to write any more

In step 4, are we directly getting the data from P3's cache or is it being written to main memory and we just read the main memory?

@beste, we are directly getting the data from P3's cache.

Please log in to leave a comment.

In the step 3, when P3 does a write to x, it should be a write-hit. Why does it need to read data from memory?