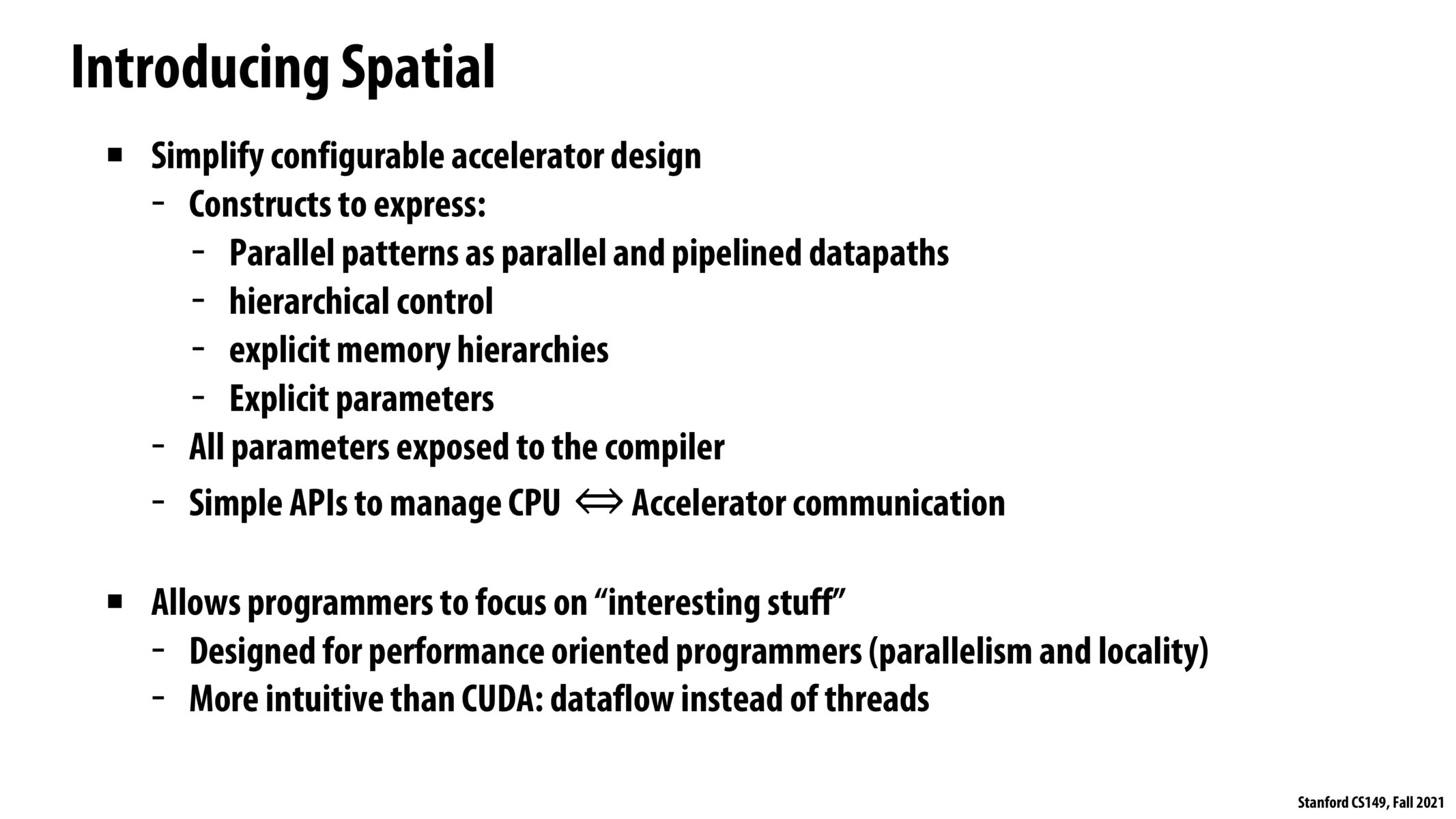

Is "more intuitive" referring to the comment made in the lecture about atomics not being necessary because we don't use threads?

@shivalgo you might find this discussion interesting (https://www.quora.com/What-is-the-difference-between-FPGA-and-CGRA) but from my understanding, the main difference is that with a course grain reconfigurable array is that you work at a "coarser" level than with a fpga, i.e. working with higher level functional blocks rather than at the register level. So I think with the CGRA you get less flexibility than an FGPA but easier programmability and I would imagine you could also get improved performance for certain applications if the functional blocks are specialized for that target domain.

@thepurplecow I think that this is getting at the idea that certain programming models are simply more intuitive to programmers – in this example, I think the point is being made that the data-parallel model is a very intuitive model because it allows programmers to think in terms of easily composable units, rather than in terms of orchestrating worker functions.

This is a good example of the principles of system design we discussed in previous lectures. It seems to have good abstractions that provide neither too little nor too much and allow programmers to work with easily composable units.

Does Spacial's compiler handle heterogenus opimizations?

If we target an FPGA does Spatial handle any potential pain points like setup times, hold times, latches, etc? Is it fundamentally creating a new design or just combining blocks that have been manually designed/tuned and then using a Verilog or similar synthesizer to handle all of the implementation on the hardware?

What does it mean by it allows programmers to focus on interesting stuff? Is it implying that, from a hardware perspective, the programmer should not have to worry about the optimization in hardware/hardware code and can solely focus on parallelism happening at the software level?

@tmdalsl Yes, this is my understanding as well!

Spatial compiles to a hardware descripted language using a two-step process. Spatial compiles to Chisel, and then Chisel generates Verilog.

I don't entirely understand the concept of hierarchical control. Could someone elaborate on this?

Please log in to leave a comment.

What is the difference between Coarse Grain Reference Architecture and FPGAs?