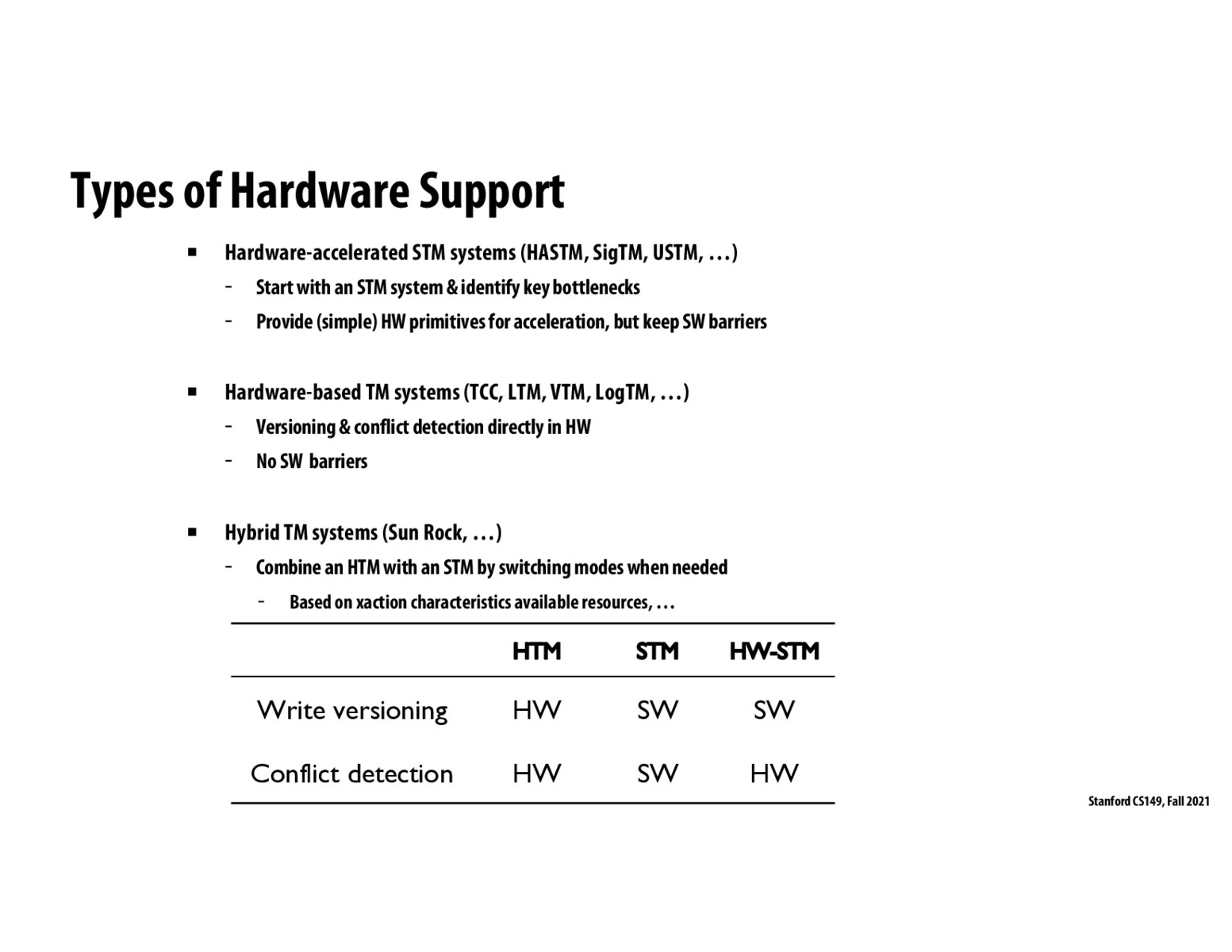

@victor I belive the second bullet point on this slide is referring a hardware-based TM that doesn't rely on any software barriers. The later slides about HW TM implementations on top of cache coherence protocol is also a example of a hardware-based TM system.

So hardware-based TM is mostly for the purpose of assisting a software-based system to speed it up? Would we ever use hardware for TM and not software?

My understanding of hardware-accelerated STM system is like 1) Softwares written in higher level programming language could implement transactional memory; it's translated to a series of machine instructions to achieve the goal of atomic, isolation, etc. 2) Yet some part of software implementation are suitable to implement on the hardware layer, in a specialized way (e.g., the HW transactions on top of cache coherence protocol above). This could makes the overall implementation faster.

Please log in to leave a comment.

So hardware-based TM is mostly for the purpose of assisting a software-based system to speed it up? Would we ever use hardware for TM and not software?