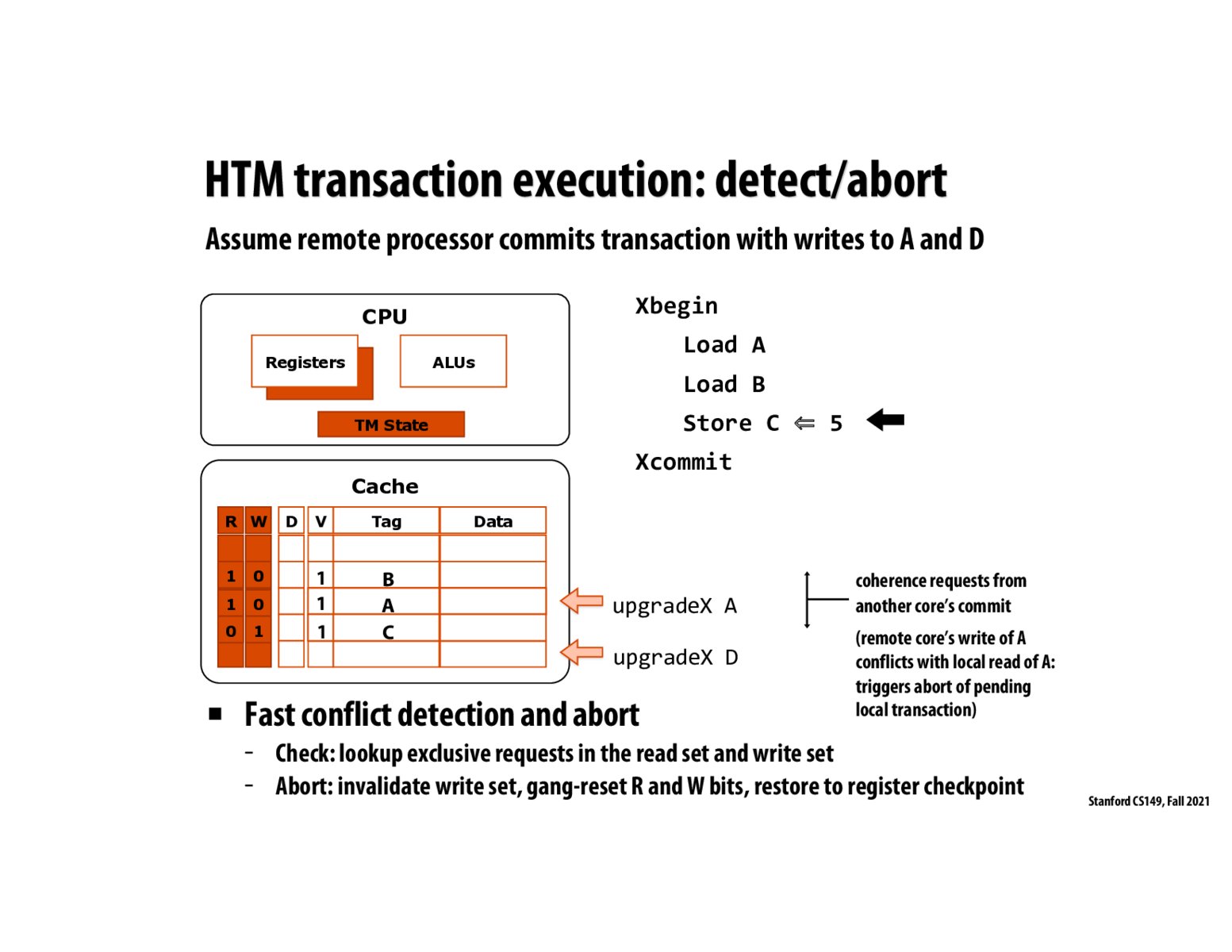

@xiyan, Yes, I believe so. When the processor aborts a transaction, it must start over from the state at the beginning of the transaction, so it has to undo all read/write bits set during transaction execution.

Do we always have to gang-reset all R and W bits? Can we only reset the bits for the addresses that are in conflict? Also, I think Kunle mentioned that if we have a write-write conflict, we might get away without an abort, since the value written by this transaction will overwrite the same memory address later. What happens to the R/W bits in this case?

@gomi, I believe we need to gang-reset all R and W bits because the transaction is being aborted, so the processor should have no record of the transaction taking place at all. However, it seems very possible to imagine an HTM implementation that only resets the bits for the conflicting addresses and keeps the other cache lines as they were so they can be reused when the transaction restarts - this would be an implementation detail though, and may require a decent amount of internal complexity (unclear whether it's "worth it").

So upon an abort, only the RW set are being cleared, while the cache entries themselves are not changed?

+1 to @kristinayige's question: do the elements stay in the cache? And in what cache state?

Should the "Data" section in the line for C have "5" in there because we're storing the value 5?

@pizza, I believe that either the cache line should be moved to the invalid state or it should be wiped out. We can't use the information in the cache since there were conflicts and we had to abort.

Please log in to leave a comment.

When the processor aborts, does the R/W bits get cleared?