hardware support for the win. looking forward to support in x86 and arm.

There's a difference between software as well as hardware support for transactional memory. Hardware support involves integrating it into our existing cache coherence protocol by introducing some extra tracking.

@crs I think it was mentioned at some point in lecture that transactional memory in general typically can perform as well as fine-grained locks

Hardware support for transactional memory is clearly quite difficult to implement correctly. Kunle mentioned that Intel had struggled with it, so looking through the wikipedia article on it, it seems they implemented support for it in 2013 on several of their chips, and then found different bugs and eventually stopped support. Although Intel announced in October 2020 that their new chip would support TSX which is transactional memory support again.

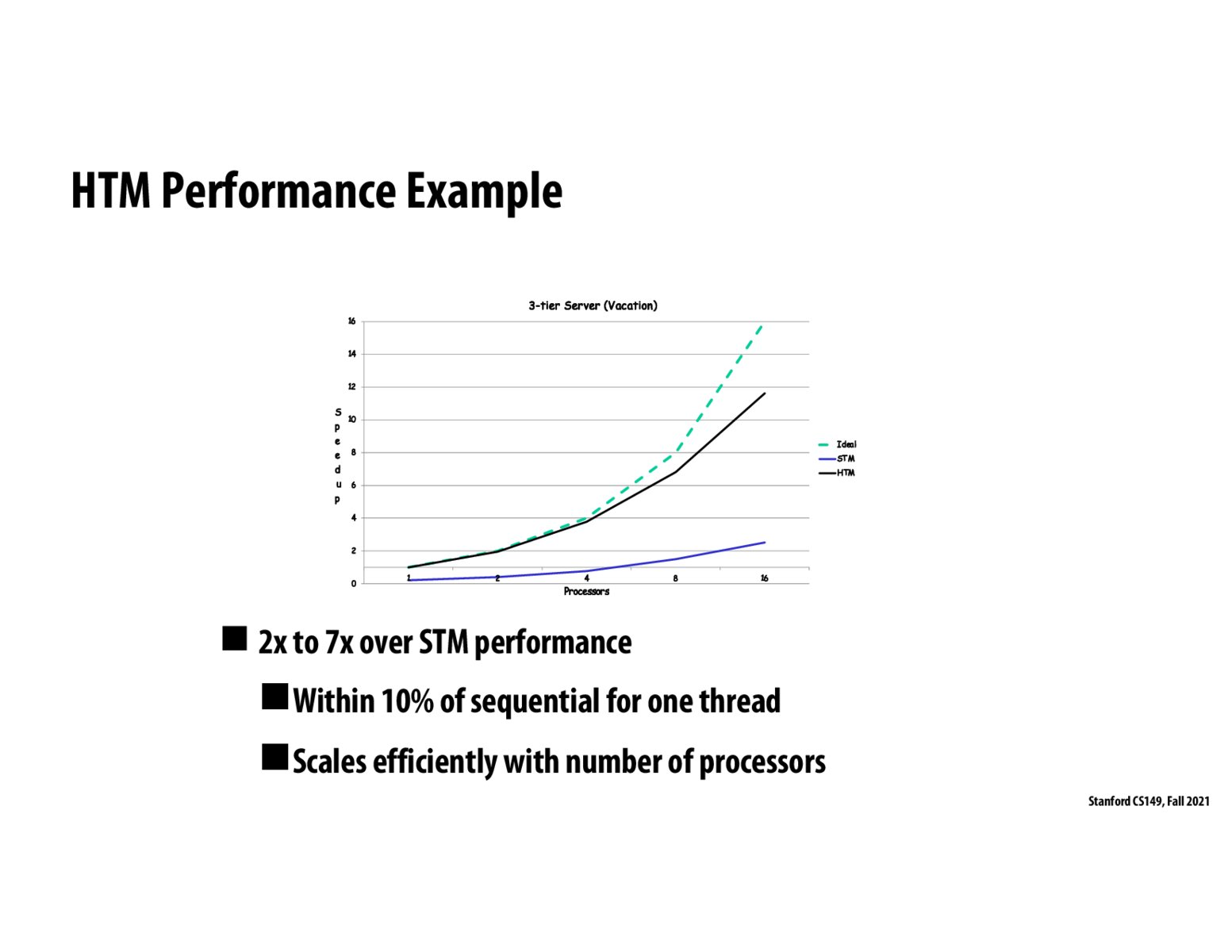

Is ideal some theoretical limit or some observed speedup? How close does H+S TM compare to this ideal line?

@mark Ideal line is theoretical limit (the y-axis speedup value corresponds 1-to-1 with x-axis number of processors). In the ideal case, we'd expect linear speedup with number of processors. However, this is often not possible due to synchronization overhead.

Looking at the graph, HTM comes pretty close to the ideal line (~100% for 4 processors and ~75% for 16 processors)

Please log in to leave a comment.

How does this compare to fine-grained locking?